# EECE416: Microcomputer and Microprocessor

source: www.mwftr.com

# 68000 Instruction and Programming Environment

# Instruction and Addressing

### **#Instruction**

- Type of function to be performed

- Location of the operand on which to perform the function

# **\*\*Addressing**

- Method to locate the operand(s)

- 2 categories

- Register Specification: the number of the register

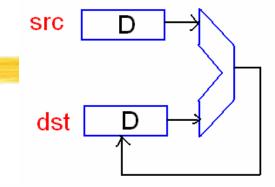

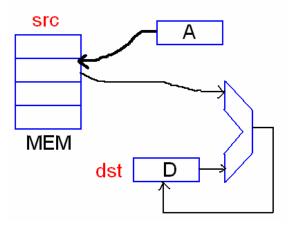

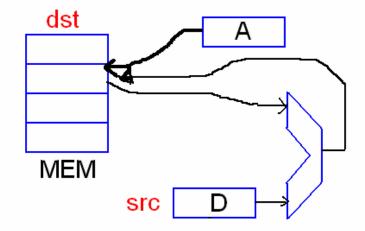

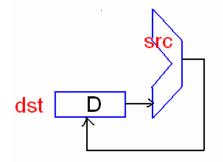

### Illustration of 3 categories

**\*\*** Register Specific Addressing

**# Memory Addressing**

**# Special Addressing**

# Instruction Format & Program EXAMPLE

### Instruction format is

### <label> opcode<.field> <operands> <;comments>

```

- <label> pointer to the instruction's memory location

- opcode operation code (i.e., MOVE, ADD)

- <.field> defines width of operands (B,W,L)

- <operands> data used in the operation

- <;comments> for program documentation

```

### LABEL OPCODE OPERAND(S) COMMENTS

```

ORG

$1000

start of PROGRAM area

#$12,d0

MOVE.L

CLR.L

d1

PROGRAM

MOVE.B data, d1

AREA

d0,d1

ADD.B

MOVE.B

d1, result

RTS

;return

$2000

start of DATA area

ORG

DATA

data

DC.B

$24

AREA

result

DS.B

;reserve a byte for result

END

$1000

; end of program and entry point

```

# RTL (Register Transfer Language)

#### 1. Notation for Operands

PC Program Counter

SR Status Register

Source Source contents

Destination Destination Contents

<> Operand data format: B, W, L

Dn Data Register n An Address Register n

Rn Any Data or Address Register

CCR Condition Code Register (Lower Byte of SR)

SP Stack Pointer (=A7)

d displacement (or "offset"): d8- eight-bit offset, d16-16-bit offset

#### Notation for sub-field and qualifier

<ea> Effective address

(<operand>) Contents of the referenced location

#xxx Immediate Data

#### 3. Notation for operations

--> Source operand is moved to the destination operand

<--> Two operands are exchanged

^ Logical AND v Logical OR

⊕ Logical Exclusive OR

Operand is logically complemented

Sign-ext Operand is sign-extended (i.e., all bits of the upper portion [Upper Byte] are made equal

to the sign-bit [msb] of the lower portion [Lower Byte]

### Examples

| Opcode | Operation                                 | Syntax                          |

|--------|-------------------------------------------|---------------------------------|

| ADD    | Source + destination>destination          | ADD <ea>, Dn</ea>               |

| ADDI   | Immediate Data + Destination> Destination | ADDI # <data>, <ea></ea></data> |

| MOVE   | Source> Destination                       | MOVE <ea>, <ea></ea></ea>       |

| NOT    | ~Destination> Destination                 | NOT <ea></ea>                   |

| SUB    | Destination – Source> Destination         | SUB <ea>, Dn</ea>               |

# RTL example

### Examples

|      | Instructio | n       | RTL            |

|------|------------|---------|----------------|

|      | MOVE.W     | #100,D0 | [D0]←100       |

|      | MOVE.W     | 100,D0  | [D0]←[M(100)]  |

|      | ADD.W      | D0,D1   | [D1]←[D1]+[D0] |

|      | MOVE.W     | D1,100  | [M(100)]←[D1]  |

| data | DC.B       | 20      | [data] ←20     |

|      | BRA        | label   | [PC] ←label    |

Notation for sub-field and qualifier

<ea> Effective address

(<operand>) Contents of the referenced location

#xxx Immediate Data

3. Notation for operations

--> Source operand is moved to the destination operand

<--> Two operands are exchanged

^ Logical AND v Logical OR

Logical Exclusive OR

Operand is logically complemented

Sign-ext Operand is sign-extended (i.e., all bits of the upper portion [Upper Byte] are made equal

to the sign-bit [msb] of the lower portion [Lower Byte]

# **ADDRESSING MODES**

- # addressing mode specifies the value of an operand, a register that contains the operand, or how to derive the effective address of an operand in memory.

- Data Reg. Direct Mode

- Address Reg. Direct Mode

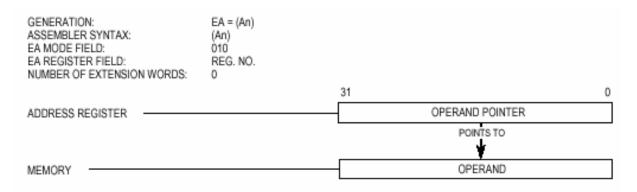

- Address Reg. Indirect Mode

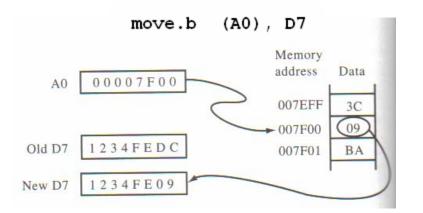

- Address Reg. Indirect with Post-increment Mode

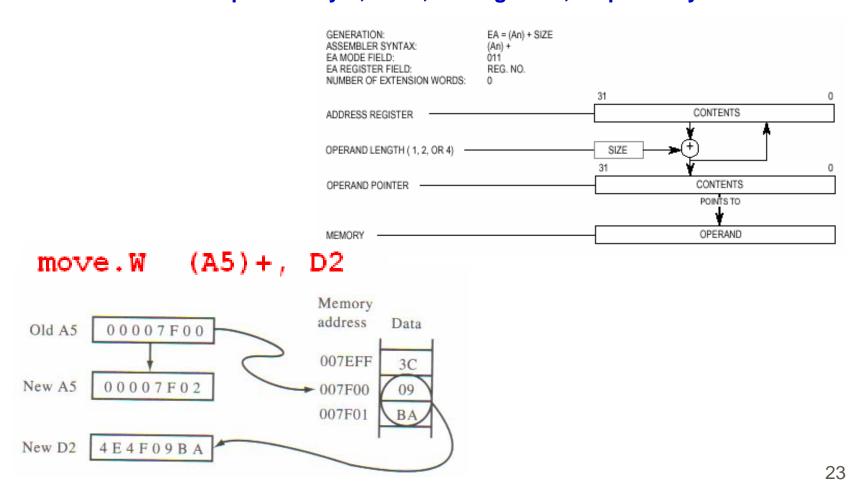

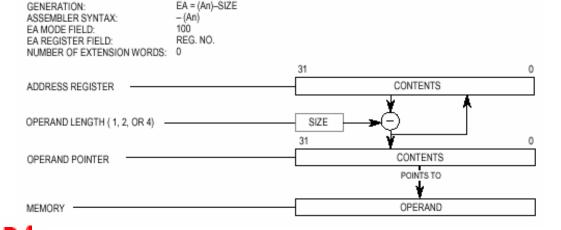

- Address Reg. Indirect with Pre-decrement Mode

- △ Address Reg. Indirect with Displacement Mode

- △ Address Reg. Indirect with Index Mode

- **△ PC Indirect with Displacement Mode**

- PC Indirect with Index Mode

- △ Absolute Short Addressing Mode

- Absolute Long Addressing Mode

# Addressing Mode Summary

| Addressing Modes                                                                                         | Syntax                                          | Mode<br>Field            | Reg.<br>Field                                | Data        | Memory      | Control     | Alterable   |

|----------------------------------------------------------------------------------------------------------|-------------------------------------------------|--------------------------|----------------------------------------------|-------------|-------------|-------------|-------------|

| Register Direct<br>Data<br>Address                                                                       | Dn<br>An                                        | 000<br>001               | reg. no.<br>reg. no.                         | <u>×</u>    | _           | _           | X<br>X      |

| Register Indirect Address Address with Postincrement Address with Predecrement Address with Displacement | (An)<br>(An)+<br>-(An)<br>(d <sub>16</sub> ,An) | 010<br>011<br>100<br>101 | reg. no.<br>reg. no.<br>reg. no.<br>reg. no. | X<br>X<br>X | X<br>X<br>X | ×<br>-<br>x | ×<br>×<br>× |

| Aoloiteas Register iroiteot of it holes<br>8 St. Majoiseament<br>Rasa Majoiseament                       | (Mg/Am/2010)<br>(Mg/Am/201)                     | 118<br>118               | rag. no.<br>rag. no.                         | X<br>X      | #<br>#      | X<br>X      | M<br>M      |

| Krogram Bornier irolisad<br>vilir Klaphnesmeni                                                           | (M <sub>18</sub> , #09)                         | 111                      | 0.10                                         | ×           | ×           | ×           |             |

| Rogram Bounter irollest with holes<br>8-85 Manisternari<br>Rasa Mayisterrari                             | (4 <sub>8.</sub>  P3.251)<br>(46. P3.251)       | 999<br>999               | 011<br>011                                   | X<br>X      | #<br>#      | X<br>X      |             |

| Progress Bounder Memory irolless)<br>Fooding speed<br>Projected                                          | ([0],[20],[27,20])<br>([0],[20],[20]            | 444<br>444               | 011<br>011                                   | X<br>X      | ä           | X<br>X      | M<br>M      |

| Absolute Data Addressing<br>Short<br>Long                                                                | (xxx).W<br>(xxx).L                              | 111<br>111               | 000<br>000                                   | X<br>X      | X<br>X      | X<br>X      | _<br>_      |

| Immediate                                                                                                | # <xxx></xxx>                                   | 111                      | 100                                          | Х           | Х           | _           | _           |

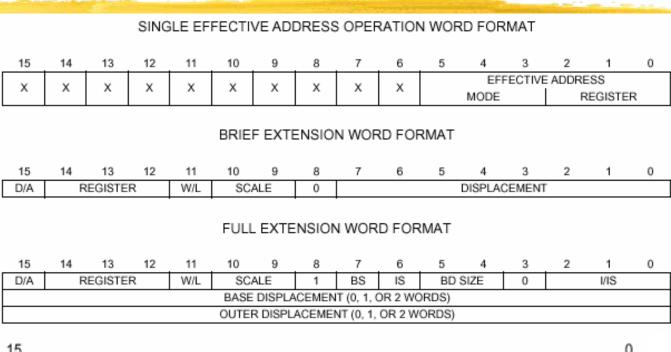

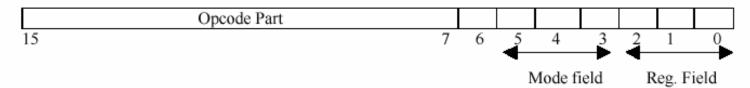

# Instruction Word (machine Code) Format

1 Word

Length:

Simple

Instruction

4 Word Length: Complex Instruction with EA extension

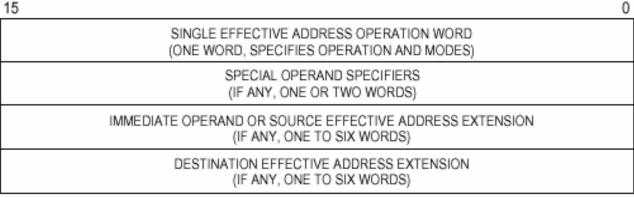

# Instruction Word Field (Opcode Bit Pattern): single word

### 1. Opcode Bit Pattern

### 2. Addressing Modes

### Selected Mnemonics

| Mnemonic | Size     | Address Mode                 | Opcode Bit Pattern<br>1111 11                                                            | Boolean                                |

|----------|----------|------------------------------|------------------------------------------------------------------------------------------|----------------------------------------|

|          |          |                              | 5432 1098 7654 3210                                                                      |                                        |

| ADD      | B/W<br>L | s=Dn<br>d=Dn<br>S=Dn<br>d=Dn | 1101 DDD1 SSEE EEEE<br>1101 DDD0 SSee eeee<br>1101 DDD1 10EE EEEE<br>1101 DDD0 10ee eeee | d+Dn→d<br>Dn+s→Dn<br>d+Dn→d<br>Dn+s→Dn |

| MOVE     | B/W<br>L |                              | 00XX RRRM MMee eeee<br>0010 RRRM MMee eeee                                               | s→d<br>s→d                             |

### Opcode Bit Pattern Codes:

### Selected items

| Code | Description                     | Code | Description               |

|------|---------------------------------|------|---------------------------|

| A    | Address Register Number         | s    | Source                    |

| D    | Data Register Number            | d    | Destination               |

| E    | Destination Effective Address   | R    | Destination Register      |

| e    | Source Effective Address        | r    | Source Register           |

| M    | Destination EA Mode             | P    | Displacement              |

| S    | Size: 00 byte, 01 Word, 10 Long | XX   | Move Size 01 byte 11 Word |

# Machine Code Example

| Mnemonic | Size     | Address Mode                 | Opcode Bit Pattern<br>1111 11<br>5432 1098 7654 3210                            | Boolean                                                                                    |

|----------|----------|------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| ADD      | B/W<br>L | s=Dn<br>d=Dn<br>S=Dn<br>d=Dn | 1101 DDD1 SSEE EEEE 1101 DDD0 SSee eeee 1101 DDD1 10EE EEEE 1101 DDD0 10ee eeee | $d+Dn\rightarrow d$<br>$Dn+s\rightarrow Dn$<br>$d+Dn\rightarrow d$<br>$Dn+s\rightarrow Dn$ |

| MOVE     | B/W<br>L |                              | 00XX RRRM MMee eeee<br>0010 RRRM MMee eeee                                      | s→d<br>s→d                                                                                 |

Table given for 68000 processor by Motorola

#### 3. Mode categories

| Type                      | Mo  | Register | Generation                    | Assembler Syntax        |

|---------------------------|-----|----------|-------------------------------|-------------------------|

|                           | de  |          |                               | _                       |

| Data Register Direct      | 000 | Reg. No. | EA=Dn                         | Dn                      |

| Address Register Direct   | 001 | Reg. No. | EA=An                         | An                      |

| Register Indirect         | 010 | Reg. No. | EA=(An)                       | (An)                    |

| Post-increment Reg. Ind.  | 011 | Reg. No. | EA=(An), An $\leftarrow$ An+N | (An)+                   |

| Pre-decrement Reg. Ind.   | 100 | Reg. No. | $An \leftarrow An-N, EA=(An)$ | -(An)                   |

| Reg. Indirect with Disp.  | 101 | Reg. No. | EA=(An)+d <sub>16</sub>       | d <sub>16</sub> (An)    |

| Indexed Reg. Ind. w/ Disp | 110 | Reg. No. | $EA=(An)+(Xn)+d_8$            | d <sub>8</sub> (An, Xn) |

| Absolute Short            | 111 | 000      | EA=(Next Word)                | XXX                     |

| Absolute Long             | 111 | 001      | EA=(Next Two Words)           | XXXXXX                  |

| PC relative with Disp.    | 111 | 010      | EA=(PC)+d <sub>16</sub>       | d <sub>16</sub> (PC)    |

| PC rel. w/ Ind. and Disp. | 111 | 011      | $EA=(PC)+(Xn)+d_8$            | d <sub>8</sub> (PC+Xn)  |

| Immediate                 | 111 | 100      | Data=Next Word(s)             | #XXX                    |

#### ADD.B D2, D3

1101 DDD0 SS eeeeee

D2 is source, D3 is destination

Therefore DDD =011 (register number 3)

SS=00, byte size

eee=000 source register mode

eee=010 source register number 2

Finally, the code is: 1101 0110 0000 0010 ---> D602

| Code   | Description                     | Code | Description               |

|--------|---------------------------------|------|---------------------------|

| A      | Address Register Number         | s    | Source                    |

| D<br>E | Data Register Number            | d    | Destination               |

| E      | Destination Effective Address   | R    | Destination Register      |

| e      | Source Effective Address        | r    | Source Register           |

| M      | Destination EA Mode             | P    | Displacement              |

| S      | Size: 00 byte, 01 Word, 10 Long | XX   | Move Size 01 byte 11 Word |

How about ADD.W D0, D1? ---->DDD=001, SS=01, ee=000, eee=000 ---->D240

## Opcode Patterns of Selected Instructions

| Mnemonic | Size | Mode  |    |    |    |    |    |    | Opco | ode B | it Pa | ttern1 |    |    |    |    |    |    | Boolean               | Cor | nditio | on C | ode | 2 |

|----------|------|-------|----|----|----|----|----|----|------|-------|-------|--------|----|----|----|----|----|----|-----------------------|-----|--------|------|-----|---|

|          |      |       | 15 | 14 | 13 | 12 | 11 | 10 | 09   | 08    | 07    | 06     | 05 | 04 | 03 | 02 | 01 | 00 |                       | Х   | N      | Ζ    | ٧   | С |

| ADD      | B/W  | s=Dn  | 1  | 1  | 0  | 1  | D  | D  | D    | 1     | S     | S      | Е  | Е  | Е  | Ε  | Е  | Ε  | d +Dn> d              | *   | *      | *    | *   | * |

|          | 1    | d=Dn  | 1  | 1  | 0  | 0  | D  | D  | D    | 0     | S     | S      | е  | е  | е  | е  | е  | е  | Dn + s>Dn             |     |        | l    |     | ı |

|          | L    | s=Dn  | 1  | 1  | 0  | 1  | D  | D  | D    | 1     | 1     | 0      | Ε  | E  | Ε  | Ε  | E  | Ε  | d + Dn>d              |     |        | l    |     | ı |

|          |      | d=Dn  | 1  | 1  | 0  | 0  | D  | D  | D    | 0     | 1     | 0      | е  | е  | е  | е  | е  | е  | Dn + s> Dn            |     |        |      |     |   |

| ADDA     | W    | d=An  | 1  | 1  | 0  | 1  | Α  | Α  | Α    | 0     | 1     | 1      | е  | е  | е  | е  | е  | е  | An + s> An            | -   | -      | -    | -   | - |

|          | L    | d=An  | 1  | 1  | 0  | 1  | Α  | Α  | Α    | 1     | 1     | 1      | е  | е  | е  | е  | е  | е  |                       |     |        |      |     |   |

| ADDI     | B/W  | s=lmm | 0  | 0  | 0  | 0  | 0  | 1  | 1    | 0     | S     | S      | Е  | Е  | Е  | Е  | Е  | Е  | d+#> d                | *   | *      | *    | *   | * |

|          | L    | s=imm | l  | l  |    | l  |    | l  |      |       |       |        | l  |    | l  | l  |    | l  |                       |     |        | l    |     | ı |

| AND      | B/W  | s=Dn  | 1  | 1  | 0  | 0  | D  | D  | D    | 1     | S     | S      | Е  | Е  | Е  | Ε  | Е  | Е  | d <and>DN&gt;d</and>  | -   | *      | *    | 0   | 0 |

|          | 1    | d=Dn  | 1  | 1  | 0  | 0  | D  | D  | D    | 0     | S     | S      | е  | е  | е  | е  | е  | е  | Dn <and>s&gt;Dn</and> |     |        | l    |     | ı |

|          | L    | s=Dn  | 1  | 1  | 0  | 0  | D  | D  | D    | 1     | 1     | 0      | Е  | Ε  | Е  | Ε  | E  | Ε  | d(and>Dn>d            |     |        | l    |     | ı |

|          | 1    | d=Dn  | 1  | 1  | 0  | 0  | D  | D  | D    | 0     | 1     | 0      | е  | е  | е  | е  | е  | е  | Dn <and>s&gt;Dn</and> |     |        | l    |     | ı |

| Bcc³     | В    |       | 0  | 1  | 1  | 0  | С  | С  | С    | С     | Р     | Р      | Р  | Р  | Р  | Р  | Р  | Р  | If CC true, then      | -   | -      | -    | -   | - |

|          | W    |       | l  | l  |    | l  |    | l  |      |       | l     |        | l  |    | l  | l  |    | l  | PC+disp> PC           |     |        | l    |     | ı |

| BRA      | В    |       | 0  | 1  | 1  | 0  | 0  | 0  | 0    | 0     | Р     | Р      | Р  | Р  | Р  | Р  | Р  | Р  | PC+disp> PC           | -   | -      | -    | -   | - |

|          | W    |       | l  | l  |    | l  |    | l  |      |       | l     |        | l  |    | l  | l  |    | l  | ,                     |     |        | l    |     | ı |

| BSR      | В    |       | 0  | 1  | 1  | 0  | 0  | 0  | 0    | 1     | Р     | Р      | Р  | Р  | Р  | Р  | Р  | Р  | PC>-(SP),             | -   | -      | -    | -   | - |

|          | W    |       | l  | l  |    | l  |    | l  |      |       | l     |        | l  |    | l  | l  |    | l  | PC+disp>PC            |     |        | l    |     | ı |

| CLR      | B/W  |       | 0  | 1  | 0  | 0  | 0  | 0  | 1    | 0     | S     | S      | Е  | Е  | Е  | Е  | Е  | Е  | 0> d                  | -   | 0      | 1    | 0   | 0 |

|          | L    |       | l  | l  |    | l  |    | l  |      |       |       |        | l  |    | l  | l  |    | l  |                       |     |        | l    |     | ı |

| CMP      | B/W  | d=Dn  | 1  | 0  | 1  | 1  | D  | D  | D    | 0     | D     | D      | е  | е  | е  | е  | е  | е  | Dn - s                | -   | *      | *    | *   | * |

|          | L    | d=Dn  | l  | l  |    | l  |    |    |      |       | l     |        | l  |    | l  | l  |    |    |                       |     |        | I    |     | 1 |

| CMPA     | B/W  | d=An  | 1  | 0  | 1  | 1  | Α  | Α  | Α    | 0     | 1     | 1      | е  | е  | е  | е  | е  | е  | An - s                | -   | *      | *    | *   | * |

|          | L    | d=An  | 1  | 0  | 1  | 1  | Α  | Α  | Α    | 1     | 1     | 1      | е  | е  | е  | е  | е  | е  |                       |     |        | l    |     | ı |

<sup>1</sup> Opcode Bit Pattern Codes:

A: Address Register Number

C: Test Condition

D: Data Register Number E: Destination Effective Address

e: Source Effective Address

M: Destination EA Mode

P: Displacement

Q: Quick Immediate Data R: Destination Register

r: Source Register

S: Size (00: B, 01: W, 10: L) XX: Move size (01:B, 11:W)

\*: Set according to result of operation

3 See Page 3, "Condition Tests" table

- : Not affected by operation

0: Cleared

1: Set

U: Undefined

| ı |          |     |   |   |   |   |   |   |   |   |   |   |   |   | ı |   |   | ı | a> PC | I |   |        |        |   |

|---|----------|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-------|---|---|--------|--------|---|

|   | MOVE     | B/W | 0 | 0 | Χ | Χ | R | R | R | M | M | M | е | е | е | е | е | е | s> d  | - | * | *      | 0      | 0 |

|   |          | L   | 0 | 0 | 1 | 0 | R | R | R | M | M | М | е | е | е | е | е | е | s> d  |   |   |        |        |   |

| ı | 1101 = 1 | 141 |   |   |   | 4 |   |   |   |   | ^ |   |   |   |   |   |   |   |       |   |   | $\neg$ | $\neg$ |   |

<sup>&</sup>lt;sup>2</sup> Condition Code Notation

## Opcode Patterns of Selected Instructions

| DIVS  | W        | d=Dn                         | 1       | 0           | 0      | 0       | D      | D      | D      | 1                | 1           | 1           | е       | е                | е       | е       | е                | е       | Dn32/s16<br>>Dn(r:q)                                                                             | - | * | * | * | 0 |

|-------|----------|------------------------------|---------|-------------|--------|---------|--------|--------|--------|------------------|-------------|-------------|---------|------------------|---------|---------|------------------|---------|--------------------------------------------------------------------------------------------------|---|---|---|---|---|

| DIVU  | W        | d=Dn                         | 1       | 0           | 0      | 0       | D      | D      | D      | 0                | 1           | 1           | е       | е                | е       | е       | е                | е       | DN32/s16<br>>DN (r:q)                                                                            | - | * | * | * | 0 |

| EOR   | B/W<br>L | s=Dn<br>s=Dn                 | 1       | 0           | 1      | 1       | r      | r      | r      | 1                | S           | S           | Е       | Ε                | Е       | Е       | Е                | Е       | d⊕Dn> d                                                                                          | - | * | * | 0 | 0 |

| JMP   | †        |                              | 0       | 1           | 0      | 0       | 1      | 1      | 1      | 0                | 1           | 1           | Е       | E                | Е       | Е       | Е                | Е       | d> PC                                                                                            | - | - | - | - | - |

| JSR   |          |                              | 0       | 1           | 0      | 0       | 1      | 1      | 1      | 0                | 1           | 0           | Е       | Е                | Е       | E       | Е                | Е       | PC> -(SP),<br>d> PC                                                                              | - | - | - | - | - |

| MOVE  | B/W      |                              | 0       | 0           | X<br>1 | X<br>0  | R<br>R | R<br>R | R<br>R | M<br>M           | M<br>M      | M           | e<br>e  | e<br>e           | e<br>e  | e<br>e  | e<br>e           | e<br>e  | s> d<br>s> d                                                                                     | - | * | * | 0 | 0 |

| MOVEA | W        |                              | 0       | 0           | 1      | 1       | A      | A      | A      | 0                | 0           | 1           | e<br>e  | e<br>e           | e<br>e  | e<br>e  | e<br>e           | e<br>e  | s> An                                                                                            | - | - | - | - | - |

| MULS  | w        | d=Dn                         | 1       | 1           | 0      | 0       | D      | D      | D      | 1                | 1           | 1           | e       | e                | e       | e       | e                | e       | Dn x s> Dn                                                                                       | - | * | * | 0 | 0 |

| MULU  | W        | d=Dn                         | 1       | 1           | 0      | 0       | D      | D      | D      | 0                | 1           | 1           | е       | е                | е       | е       | е                | е       | Dn x s> Dn                                                                                       | - | * | * | 0 | 0 |

| NEG   | B/W      |                              | 0       | 1           | 0      | 0       | 0      | 1      | 0      | 0                | S           | S           | Е       | E                | Е       | E       | Е                | Е       | 0 – d> d                                                                                         | * | * | * | * | * |

| NOT   | B/W<br>L |                              | 0       | 1           | 0      | 0       | 0      | 1      | 1      | 0                | S           | S           | Е       | Е                | Е       | Ε       | Е                | Е       | ~d> d                                                                                            | - | * | * | 0 | 0 |

| OR    | B/W<br>L | s=Dn<br>d=Dn<br>s=Dn<br>d=Dn | 1 1 1 1 | 0<br>0<br>0 | 0 0 0  | 0 0 0   | 0 0 0  | 0 0 0  | D D D  | 1<br>0<br>1<br>0 | S<br>S<br>1 | S<br>S<br>0 | E e E e | E<br>e<br>E<br>e | E e E e | E e E e | E<br>e<br>E<br>e | E e E e | d <or>Dn&gt; d<br/>Dn <or> s&gt; Dn<br/>d <or> Dn&gt; d<br/>DN <or> s&gt; Dn</or></or></or></or> | - | * | * | 0 | 0 |

| RTS   | +        | u - D 11                     | Ö       | 1           | 0      | ő       | 1      | 1      | 1      | 0                | Ó           | 1           | 1       | 1                | ō       | 1       | 0                | 1       | (SP)+> PC                                                                                        | - | - | - | - | - |

| SUB   | B/W<br>L | s=Dn<br>d=Dn<br>s=Dn<br>d=Dn | 1 1 1 1 | 0 0 0       | 0 0 0  | 1 1 1 1 | 0000   | 0000   | 0 0 0  | 1<br>0<br>1<br>0 | S S 1       | S<br>S<br>0 | E e E e | E e E e          | E e E e | E e E e | E e E e          | E e E e | d – Dn>d<br>Dn – s> Dn<br>d – Dn>< d<br>Dn – s> Dn                                               | * | * | * | * | * |

| SUBA  | w        | d=An<br>d=An                 | 1       | 0           | 0      | 1       | A      | A      | A      | 0                | 1           | 1           | e<br>e  | e<br>e           | e<br>e  | e<br>e  | e<br>e           | e<br>e  | An – s> An                                                                                       | - | - | - | - | - |

| SWAP  | W        | u-AII                        | ò       | 1           | 0      | 0       | 1      | 0      | 0      | 0                | 0           | 1           | 0       | 0                | 0       | D       | D                | D       | Dn(31:16)<br><>DN(15:0)                                                                          | - | * | * | 0 | 0 |

| TRAP  |          |                              | 0       | 1           | 0      | 0       | 1      | 1      | 1      | 0                | 0           | 1           | 1       | 1                | 0       | 1       | 1                | 1       | PC> -(SSP),<br>SR> -(SSP),<br>(trap vector)><br>PC                                               | - | - | - | - | - |

| TST   | B/W<br>L |                              | 0       | 1           | 0      | 0       | 1      | 0      | 1      | 0                | S           | S           | Е       | Е                | Е       | Е       | Е                | Е       | test d> cc                                                                                       | - | * | * | 0 | 0 |

# Machine Code Example 2

|                                     |      |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | u> FO |

|-------------------------------------|------|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-------|

|                                     | MOVE | 3/W | 0 | 0 | Х | Х | R | R | R | M | M | Μ | е | е | е | е | е | е | s> d  |

| L   0 0 1 0 R R R M M M e e e e e e |      | .   | 0 | 0 | 1 | 0 | R | R | R | M | M | М | е | е | е | е | е | е | s> d  |

#### 1 Opcode Bit Pattern Codes:

A: Address Register Number M: Destination EA Mode

C: Test Condition P: Displacement

XX: Move size (01:B, 11:W)

D: Data Register Number E: Destination Effective Address Q: Quick Immediate Data R: Destination Register

e: Source Effective Address

r: Source Register

S: Size (00: B. 01: W. 10: L)

Mode categories

| Type                      | Mo  | Register | Generation                    | Assembler Syntax        |

|---------------------------|-----|----------|-------------------------------|-------------------------|

|                           | de  |          |                               |                         |

| Data Register Direct      | 000 | Reg. No. | EA=Dn                         | Dn                      |

| Address Register Direct   | 001 | Reg. No. | EA=An                         | An                      |

| Register Indirect         | 010 | Reg. No. | EA=(An)                       | (An)                    |

| Post-increment Reg. Ind.  | 011 | Reg. No. | EA=(An), An $\leftarrow$ An+N | (An)+                   |

| Pre-decrement Reg. Ind.   | 100 | Reg. No. | An ←An-N, EA=(An)             | -(An)                   |

| Reg. Indirect with Disp.  | 101 | Reg. No. | EA=(An)+d <sub>16</sub>       | d <sub>16</sub> (An)    |

| Indexed Reg. Ind. w/ Disp | 110 | Reg. No. | $EA=(An)+(Xn)+d_8$            | d <sub>8</sub> (An, Xn) |

| Absolute Short            | 111 | 000      | EA=(Next Word)                | XXX                     |

| Absolute Long             | 111 | 001      | EA=(Next Two Words)           | XXXXXX                  |

| PC relative with Disp.    | 111 | 010      | EA=(PC)+d <sub>16</sub>       | d <sub>16</sub> (PC)    |

| PC rel. w/ Ind. and Disp. | 111 | 011      | $EA=(PC)+(Xn)+d_8$            | d <sub>8</sub> (PC+Xn)  |

| Immediate                 | 111 | 100      | Data=Next Word(s)             | #XXX                    |

```

\Re Move.w (A0), D0 \rightarrow00xx RRRMMM

eeeeee

010000 \rightarrow 3010

\rightarrow0011

000000

010000 \rightarrow 1010

\# Move.B (A0), D0 \rightarrow0001

000000

\# Move.W (A1), D1 \rightarrow 0011

001000

010001 \rightarrow 3211

\# Move.B (A1), D1 \rightarrow 0001 001000

010001 \rightarrow 3

```

# Machine Code Example 3

| MEMORY MACHINE LOCATION CODE |           | ASSEMBLY<br>CODE | (         |

|------------------------------|-----------|------------------|-----------|

|                              | ~         |                  |           |

| 00001000                     | 1         | ORG              | \$1000    |

| 00001000 203C 00000012       | 2         | MOVE.L           | #\$12,d0  |

| 00001006 4281                | 3         | CLR.L            | d1        |

| 00001008 1239 00002000       | 4         | MOVE.B           | data,d1   |

| 0000100E D200                | 5         | ADD.B            | d0,d1     |

| 00001010 13C1 00002001       | 6         | MOVE.B           | d1,result |

| 00001016 4E75                | 7         | RTS              |           |

|                              | 8         |                  |           |

| 00002000                     | 9         | ORG              | \$2000    |

| 00002000 24                  | 10 data   | DC.B             | \$24      |

| 00002001                     | 11 result | DS.B             | 1         |

| 00002002                     | 12        | END              | \$1000    |

| ASSEMBLY CODE   | INS  | TRUC   | TION  | FORM | IAT | MACHINE CODE  |

|-----------------|------|--------|-------|------|-----|---------------|

| MOVE.L #\$12,d0 | 00 1 | 10 000 | 000   | 111  | 100 | 203C 00000012 |

| MOVE.B data, d1 | 00 0 | 01 00  | . 000 | 111  | 001 | 1239 00002000 |

### FULL EXTENSION WORD FORMAT

|   | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |                                       |  |  |  |  |     | Ó |    |    |      |      |   |  |      |  |

|---|---------------------------------------|---------------------------------------|--|--|--|--|-----|---|----|----|------|------|---|--|------|--|

| ſ | D/A REGISTER W/L                      |                                       |  |  |  |  | \LE | 1 | BS | IS | BD S | SIZE | 0 |  | I/IS |  |

|   |                                       | BASE DISPLACEMENT (0, 1, OR 2 WORDS)  |  |  |  |  |     |   |    |    |      |      |   |  |      |  |

| ſ |                                       | OUTER DISPLACEMENT (0, 1, OR 2 WORDS) |  |  |  |  |     |   |    |    |      |      |   |  |      |  |

|      |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | u == / F O |

|------|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|------------|

| MOVE | B/W | 0 | 0 | Х | Х | R | R | R | M | M | М | е | е | е | е | е | е | s> d       |

|      | L   | 0 | 0 | 1 | 0 | R | R | R | M | M | М | е | е | е | е | е | е | s> d       |

|      |     | - | - |   |   |   |   |   | - | - |   |   |   |   |   |   |   |            |

### 1 Opcode Bit Pattern Codes:

A: Address Register Number M: Destination EA Mode

C: Test Condition

D: Data Register Number E: Destination Effective Address

e: Source Effective Address

P: Displacement

Q: Quick Immediate Data R: Destination Register

r: Source Register

S: Size (00: B, 01: W, 10: L)

XX: Move size (01:B, 11:W)

#### 3. Mode categories

| Type                      | Mo  | Register | Generation                    | Assembler Syntax        |

|---------------------------|-----|----------|-------------------------------|-------------------------|

|                           | de  |          |                               |                         |

| Data Register Direct      | 000 | Reg. No. | EA=Dn                         | Dn                      |

| Address Register Direct   | 001 | Reg. No. | EA=An                         | An                      |

| Register Indirect         | 010 | Reg. No. | EA=(An)                       | (An)                    |

| Post-increment Reg. Ind.  | 011 | Reg. No. | EA=(An), An $\leftarrow$ An+N | (An)+                   |

| Pre-decrement Reg. Ind.   | 100 | Reg. No. | $An \leftarrow An-N, EA=(An)$ | -(An)                   |

| Reg. Indirect with Disp.  | 101 | Reg. No. | EA=(An)+d <sub>16</sub>       | d <sub>16</sub> (An)    |

| Indexed Reg. Ind. w/ Disp | 110 | Reg. No. | $EA=(An)+(Xn)+d_8$            | d <sub>8</sub> (An, Xn) |

| Absolute Short            | 111 | 000      | EA=(Next Word)                | XXX                     |

| Absolute Long             | 111 | 001      | EA=(Next Two Words)           | XXXXXX                  |

| PC relative with Disp.    | 111 | 010      | EA=(PC)+d <sub>16</sub>       | d <sub>16</sub> (PC)    |

| PC rel. w/ Ind. and Disp. | 111 | 011      | EA=(PC)+(Xn)+d <sub>8</sub>   | d <sub>8</sub> (PC+Xn)  |

| Immediate                 | 111 | 100      | Data=Next Word(s)             | #XXX                    |

| \$001000 | 20  | 3C  |

|----------|-----|-----|

| \$001002 | 0.0 | 0.0 |

| \$001004 | 0.0 | 12  |

| \$001006 | 42  | 81  |

| \$001008 | 12  | 39  |

| \$00100A | 00  | 0.0 |

| \$00100C | 20  | 0.0 |

| \$00100E | D2  | 0.0 |

| \$001010 | 13  | Cl  |

| \$001012 | 0.0 | 0.0 |

| \$001014 | 20  | 01  |

| \$001016 | 4E  | 75  |

|          |     |     |

|          | data | result |

|----------|------|--------|

| \$002000 | 20   | 0.0    |

| ASSEMBLY CODE   | INSTRUCTION FORMAT    | MACHINE CODE  |

|-----------------|-----------------------|---------------|

| MOVE.L #\$12,d0 | 00 10 000 000 111 100 | 203C 00000012 |

| MOVE.B data, d1 | 00 01 001 000 111 001 | 1239 00002000 |

# Machine Code Test

**#**1. MOVE.B D2, D3

```

3. MOVE.B #$35, D23. MOVE.B D1, (A1) +4. MOVE.B (A2) +, D7

```

```

SS: 00(B), 01(W), 10(L)

RRR: Dst Req

eeeeee: Src EA (Mode+ Req.No)

EEEEEEE: Dst EA (Mode+Req. No)

MMM: Dst EA Mode

Mode + Req. No

000nnn

\mathbf{D}\mathbf{n}

An

001nnn

010nnn

(An)

(An)+

011nnn

Imm

111100

Solution

MOVE.B D2, D3

00XXRRRMMMeeeeee

0001011000000010 --> 1602

D3

D_2

```

# **Instruction Summary**

| Opcode      | Operation                                                                                                                                                                                        | Syntax                                                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| ABCD        | $Source_{10} + Destination_{10} + X \to Destination$                                                                                                                                             | ABCD Dy,Dx<br>ABCD –(Ay), –(Ax)                       |

| ADD         | Source + Destination → Destination                                                                                                                                                               | ADD <ea>,Dn<br/>ADD Dn,<ea></ea></ea>                 |

| ADDA        | Source + Destination → Destination                                                                                                                                                               | ADDA <ea>,An</ea>                                     |

| ADDI        | Immediate Data + Destination $\rightarrow$ Destination                                                                                                                                           | ADDI# <data>,<ea></ea></data>                         |

| ADDQ        | Immediate Data + Destination → Destination                                                                                                                                                       | ADDQ # <data>,<ea></ea></data>                        |

| ADDX        | Source + Destination + $X \rightarrow$ Destination                                                                                                                                               | ADDX Dy, Dx<br>ADDX –(Ay), –(Ax)                      |

| AND         | Source $\Lambda$ Destination $\rightarrow$ Destination                                                                                                                                           | AND <ea>,Dn<br/>AND Dn,<ea></ea></ea>                 |

| ANDI        | Immediate Data $\Lambda$ Destination $\rightarrow$ Destination                                                                                                                                   | ANDI# <data>, <ea></ea></data>                        |

| ANDI to CCR | Source $\Lambda$ CCR $\rightarrow$ CCR                                                                                                                                                           | ANDI# <data>, CCR</data>                              |

| ANDI to SR  | If supervisor state then Source $\Lambda$ SR $\to$ SR else TRAP                                                                                                                                  | ANDI # <data>, SR</data>                              |

| ASL, ASR    | Destination Shifted by <count> → Destination</count>                                                                                                                                             | ASd Dx,Dy<br>ASd # <data>,Dy<br/>ASd <ea></ea></data> |

| Bcc         | If (condition true) then PC $+ d \rightarrow PC$                                                                                                                                                 | Bcc <label></label>                                   |

| BCHG        | $\sim$ ( <number> of Destination) <math>\rightarrow</math> Z;<br/><math>\sim</math> (<number> of Destination) <math>\rightarrow</math> <br/> <br/> <br/> <br/> for Destination</number></number> | BCHG Dn, <ea><br/>BCHG # <data>,<ea></ea></data></ea> |

| BCLR        | $\sim$ (<br>bit number> of Destination) $\rightarrow$ Z;<br>0 $\rightarrow$<br>bit number> of Destination                                                                                        | BCLR Dn, <ea><br/>BCLR # <data>,<ea></ea></data></ea> |

| BKPT        | Run breakpoint acknowledge cycle;<br>TRAP as illegal instruction                                                                                                                                 | BKPT # <data></data>                                  |

| BRA         | $PC + d \rightarrow PC$                                                                                                                                                                          | BRA <label></label>                                   |

| BSET        | ~ ( <bit number=""> of Destination) → Z;<br/>1 → <bit number=""> of Destination</bit></bit>                                                                                                      | BSET Dn, <ea><br/>BSET #<data>,<ea></ea></data></ea>  |

| BSR         | $SP-4\toSP;PC\to(SP);PC+d\toPC$                                                                                                                                                                  | BSR <label></label>                                   |

| BTST        | – ( <bit number=""> of Destination) <math>\rightarrow</math> Z;</bit>                                                                                                                            | BTST Dn, <ea><br/>BTST # <data>,<ea></ea></data></ea> |

| CHK         | If Dn < 0 or Dn > Source then TRAP                                                                                                                                                               | CHK <ea>,Dn</ea>                                      |

| CLR         | 0 → Destination                                                                                                                                                                                  | CLR <es></es>                                         |

| CMP         | Destination—Source → cc                                                                                                                                                                          | CMP <ea>,Dn</ea>                                      |

| CMPA        | Destination—Source                                                                                                                                                                               | CMPA <ea>,An</ea>                                     |

| CMPI        | Destination —Immediate Data                                                                                                                                                                      | CMPI# <data>,<ea></ea></data>                         |

| CMPM        | Destination—Source → cc                                                                                                                                                                          | CMPM (Ay)+, (Ax)+                                     |

| DBcc        | If condition false then (Dn $-1 \rightarrow$ Dn;<br>If Dn $\neq$ $-1$ then PC + d $\rightarrow$ PC)                                                                                              | DBcc Dn, <label></label>                              |

| Opcode           | Operation                                                                                                                                                                                                                                                                                                                                           | Syntax                                                                                      |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| DIVS             | Destination/Source → Destination                                                                                                                                                                                                                                                                                                                    | DIVS.W <ea>,Dn 32/16 → 16r:16q</ea>                                                         |

| DIVU             | Destination/Source → Destination                                                                                                                                                                                                                                                                                                                    | DIVU.W <ea>,Dn 32/16 → 16r:16q</ea>                                                         |

| EOR              | Source ⊕ Destination → Destination                                                                                                                                                                                                                                                                                                                  | EOR Dn, <ea>&gt;</ea>                                                                       |

| EORI             | Immediate Data ⊕ Destination → Destination                                                                                                                                                                                                                                                                                                          | EORI# <data>,<ea></ea></data>                                                               |

| EORI to CCR      | Source ⊕ CCR → CCR                                                                                                                                                                                                                                                                                                                                  | EORI# <data>,CCR</data>                                                                     |

| EORI to SR       | If supervisor state then Source ⊕SR → SR else TRAP                                                                                                                                                                                                                                                                                                  | EORI# <data>,SR</data>                                                                      |

| EXG              | $Rx \leftrightarrow Ry$                                                                                                                                                                                                                                                                                                                             | EXG Dx,Dy<br>EXG Ax,Ay<br>EXG Dx,Ay<br>EXG Ay,Dx                                            |

| EXT              | Destination Sign-Extended → Destination                                                                                                                                                                                                                                                                                                             | EXT.W Dn extend byte to word<br>EXT.L Dn extend word to long word                           |

| ILLEGAL          | $\begin{array}{l} \text{SSP} - 2 \rightarrow \text{SSP}; \text{Vector Offset} \rightarrow (\text{SSP}); \\ \text{SSP} - 4 \rightarrow \text{SSP}; \text{PC} \rightarrow (\text{SSP}); \\ \text{SSP} - 2 \rightarrow \text{SSP}; \text{SR} \rightarrow (\text{SSP}); \\ \text{Illegal Instruction Vector Address} \rightarrow \text{PC} \end{array}$ | ILLEGAL                                                                                     |

| JMP              | Destination Address → PC                                                                                                                                                                                                                                                                                                                            | JMP <ea></ea>                                                                               |

| JSR              | $SP - 4 \rightarrow SP$ ; $PC \rightarrow (SP)$<br>Destination Address $\rightarrow PC$                                                                                                                                                                                                                                                             | JSR <ea></ea>                                                                               |

| LEA              | <ea> → An</ea>                                                                                                                                                                                                                                                                                                                                      | LEA <ea>,An</ea>                                                                            |

| LINK             | $SP - 4 \rightarrow SP$ ; $An \rightarrow (SP)$<br>$SP \rightarrow An$ , $SP + d \rightarrow SP$                                                                                                                                                                                                                                                    | LINK An, # <displacement></displacement>                                                    |

| LSL,LSR          | Destination Shifted by <count> → Destination</count>                                                                                                                                                                                                                                                                                                | LSd <sup>1</sup> Dx,Dy<br>LSd <sup>1</sup> # <data>,Dy<br/>LSd<sup>1</sup> <ea></ea></data> |

| MOVE             | Source → Destination                                                                                                                                                                                                                                                                                                                                | MOVE <ea>,<ea></ea></ea>                                                                    |

| MOVEA            | Source → Destination                                                                                                                                                                                                                                                                                                                                | MOVEA <ea>,An</ea>                                                                          |

| MOVE from<br>CCR | CCR → Destination                                                                                                                                                                                                                                                                                                                                   | MOVE CCR, <ea>&gt;</ea>                                                                     |

| MOVE to<br>CCR   | Source → CCR                                                                                                                                                                                                                                                                                                                                        | MOVE <ea>,CCR</ea>                                                                          |

| MOVE from<br>SR  | SR → Destination If supervisor state then SR → Destination else TRAP (MC68010 only)                                                                                                                                                                                                                                                                 | MOVE SR, <ea>&gt;</ea>                                                                      |

| MOVE to SR       | If supervisor state then Source → SR else TRAP                                                                                                                                                                                                                                                                                                      | MOVE <ea>,SR</ea>                                                                           |

# **Instruction Summary**

| Opcode        | Operation                                                                                            | Syntax                                                                                         |  |  |

|---------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|

| MOVE USP      | If supervisor state then USP $\rightarrow$ An or An $\rightarrow$ USP else TRAP                      | MOVE USP An<br>MOVE An, USP                                                                    |  |  |

| MOVEC         | If supervisor state then $Rc \rightarrow Rn$ or $Rn \rightarrow Rc$ else $TRAP$                      | MOVEC Rc,Rn<br>MOVEC Rn,Rc                                                                     |  |  |

| MOVEM         | $ \begin{array}{l} Registers \to Destination \\ Source \to Registers \end{array} $                   | MOVEM register list, <ea><br/>MOVEM <ea>,register list</ea></ea>                               |  |  |

| MOVEP         | Source → Destination                                                                                 | MOVEP Dx,(d,Ay)<br>MOVEP (d,Ay),Dx                                                             |  |  |

| MOVEQ         | $Immediate\ Data \rightarrow Destination$                                                            | MOVEQ # <data>,Dn</data>                                                                       |  |  |

| MOVES         | If supervisor state then Rn $ ightarrow$ Destination [DFC] or Source [SFC] $ ightarrow$ Rn else TRAP | MOVES Rn, <ea><br/>MOVES <ea>,Rn</ea></ea>                                                     |  |  |

| MULS          | $Source \times Destination \to Destination$                                                          | MULS.W <ea>,Dn 16 x 16 → 32</ea>                                                               |  |  |

| MULU          | $Source \times Destination \to Destination$                                                          | MULU.W <ea>,Dn 16 x 16 → 32</ea>                                                               |  |  |

| NBCD          | 0 - (Destination <sub>10</sub> ) - X → Destination                                                   | NBCD <ea></ea>                                                                                 |  |  |

| NEG           | 0 - (Destination) → Destination                                                                      | NEG <ea></ea>                                                                                  |  |  |

| NEGX          | 0 – (Destination) – X → Destination                                                                  | NEGX <ea>&gt;</ea>                                                                             |  |  |

| NOP           | None                                                                                                 | NOP                                                                                            |  |  |

| NOT           | ~Destination → Destination                                                                           | NOT <ea></ea>                                                                                  |  |  |

| OR            | Source V Destination → Destination                                                                   | OR <ea>,Dn<br/>OR Dn,<ea></ea></ea>                                                            |  |  |

| ORI           | Immediate Data V Destination → Destination                                                           | ORI# <data>,<ea></ea></data>                                                                   |  |  |

| ORI to CCR    | Source V CCR $\rightarrow$ CCR                                                                       | ORI# <data>,CCR</data>                                                                         |  |  |

| ORI to SR     | If supervisor state then Source V SR → SR else TRAP                                                  | ORI # <data>,SR</data>                                                                         |  |  |

| PEA           | $Sp-4 \rightarrow SP$ ; $\leq ea \geq \rightarrow (SP)$                                              | PEA <ea>&gt;</ea>                                                                              |  |  |

| RESET         | If supervisor state<br>then Assert RESET Line<br>else TRAP                                           | RESET                                                                                          |  |  |

| ROL, ROR      | Destination Rotated by <count> → Destination</count>                                                 | ROd <sup>1</sup> Rx,Dy<br>ROd <sup>1</sup> # <data>,Dy<br/>ROd<sup>1</sup> <ea></ea></data>    |  |  |

| ROXL,<br>ROXR | Destination Rotated with X by <count> → Destination</count>                                          | ROXd <sup>1</sup> Dx,Dy<br>ROXd <sup>1</sup> # <data>,Dy<br/>ROXd<sup>1</sup> <ea></ea></data> |  |  |

| RTD           | (SP) → PC; SP + 4 + d → SP                                                                           | RTD # <displacement></displacement>                                                            |  |  |

| Opcode | Operation                                                                                                                                                                                                                                                                                                                  | Syntax                                |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| RTE    | If supervisor state then (SP) $\rightarrow$ SR; SP + 2 $\rightarrow$ SP; (SP) $\rightarrow$ PC; SP + 4 $\rightarrow$ SP; restore state and deallocate stack according to (SP) else TRAP                                                                                                                                    | RTE                                   |

| RTR    | $(SP) \rightarrow CCR; SP + 2 \rightarrow SP;$<br>$(SP) \rightarrow PC; SP + 4 \rightarrow SP$                                                                                                                                                                                                                             | RTR                                   |

| RTS    | $(SP) \rightarrow PC$ ; $SP + 4 \rightarrow SP$                                                                                                                                                                                                                                                                            | RTS                                   |

| SBCD   | $Destination_{10} - Source_{10} - X \to Destination$                                                                                                                                                                                                                                                                       | SBCD Dx,Dy<br>SBCD -(Ax),-(Ay)        |

| Scc    | If condition true then 1s → Destination else 0s → Destination                                                                                                                                                                                                                                                              | Scc <ea></ea>                         |

| STOP   | If supervisor state then immediate Data → SR; STOP else TRAP                                                                                                                                                                                                                                                               | STOP # <data></data>                  |

| SUB    | Destination – Source → Destination                                                                                                                                                                                                                                                                                         | SUB <ea>,Dn<br/>SUB Dn,<ea></ea></ea> |

| SUBA   | Destination – Source → Destination                                                                                                                                                                                                                                                                                         | SUBA <ea>,An</ea>                     |

| SUBI   | $Destination - Immediate \; Data \to Destination$                                                                                                                                                                                                                                                                          | SUBI# <data>,<ea></ea></data>         |

| SUBQ   | ${\sf Destination-Immediate\ Data\ } \to {\sf Destination}$                                                                                                                                                                                                                                                                | SUBQ # <data>,<ea></ea></data>        |

| SUBX   | ${\sf Destination-Source-X} \to {\sf Destination}$                                                                                                                                                                                                                                                                         | SUBX Dx,Dy<br>SUBX -(Ax),-(Ay)        |

| SWAP   | Register [31:16] ↔ Register [15:0]                                                                                                                                                                                                                                                                                         | SWAP Dn                               |

| TAS    | Destination Tested → Condition Codes; 1 → bit 7 of<br>Destination                                                                                                                                                                                                                                                          | TAS <ea></ea>                         |

| TRAP   | $\begin{array}{l} \text{SSP} - 2 \rightarrow \text{SSP}; \text{Format/Offset} \rightarrow (\text{SSP}); \\ \text{SSP} - 4 \rightarrow \text{SSP}; \text{PC} \rightarrow (\text{SSP}); \text{SSP-2} \rightarrow \text{SSP}; \\ \text{SR} \rightarrow (\text{SSP}); \text{Vector Address} \rightarrow \text{PC} \end{array}$ | TRAP # <vector></vector>              |

| TRAPV  | If V then TRAP                                                                                                                                                                                                                                                                                                             | TRAPV                                 |

| TST    | Destination Tested $\rightarrow$ Condition Codes                                                                                                                                                                                                                                                                           | TST <ea></ea>                         |

| UNLK   | $An \rightarrow SP$ ; $(SP) \rightarrow An$ ; $SP + 4 \rightarrow SP$                                                                                                                                                                                                                                                      | UNLK An                               |

# Data Reg.Direct Mode

the effective address field specifies the data register containing the operand.

GENERATION: EA = Dn

ASSEMBLER SYNTAX: Dn

EA MODE FIELD: 000

EA REGISTER FIELD: REG. NO.

NUMBER OF EXTENSION WORDS: 0

DATA REGISTER OPERAND

move.W D3, D4 ;D3 source, D4 destination

Before: D3 = 100030FE

D4=8E552900

After: D3=100030FE

D4=8E5530FE

# Address Reg. Direct Mode

The effective address field specifies the address register containing the operand.

GENERATION:

EA = An

ASSEMBLER SYNTAX:

An

EA MODE FIELD:

001

EA REGISTER FIELD:

REG. NO.

NUMBER OF EXTENSION WORDS:

0

ADDRESS REGISTER OPERAND

Address Register Mode involves, usually, 32-bit (Long Word) operation. Since Address is expressed by a Long Word.

movea.L A5, A2

;After the operation (A5)=(A2)

When, in address register mode, size in NOT in long word: the EA's upper word is determined by the "sign extended from lower word"

EXample:

Before: A0=00006800

A1=0000C580

movea.W A0, A2 After: A2=00006800

movea.W A1, A2 After: A2=FFFFC580

"Short Addressing" --fast access inside the range Word operation, instead of Long Word Operation

# Address Reg. Indirect Mode

# The effective address field specifies the address register containing the address of the operand in memory.

What would be the content of D7 after

move.W (A0), D7 ?

# Address Reg. Indirect with Post-increment Mode

- Herefrective address field specifies the address register containing the address of the operand in memory.

- After the operand address is used, it is incremented by one, two, or four depending on the size of the operand: byte, word, or long word, respectively.

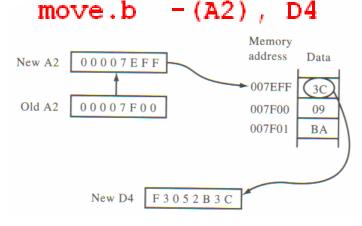

### **Address Register Indirect with Pre-decrement Mode**

The effective address field specifies the address register containing the address of the operand in memory.

Before the operand address is used, it is decremented by **one**, **two**, **or four** depending on the operand size: **byte**, **word**, **or long word**,

respectively.

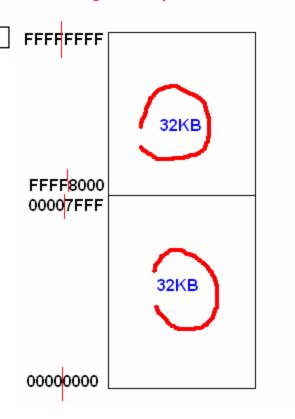

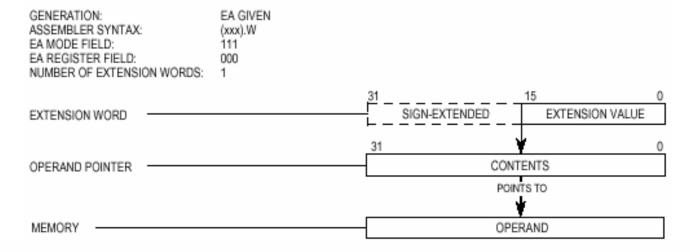

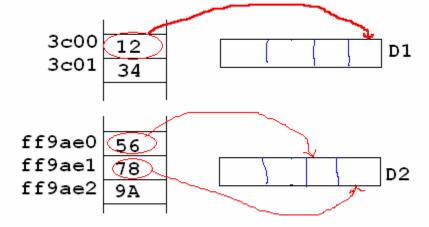

## **Absolute Short Addressing Mode**

- # the address of the operand is in the extension word.

- # The 16-bit address is sign-extended to 32 bits before it is used.

### Example:

move.b \$3C00, d1

MOVE.W \$9AEO, D2

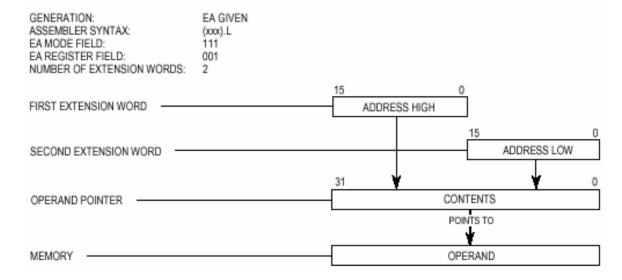

## **Absolute Long Addressing Mode**

- # the operand's address occupies the two extension words following the instruction word in memory.

- ## The first extension word contains the high-order part of the address; the second contains the low-order part of the address.

move.b \$2e000, D0

# **Immediate Mode**

# #the operand is in one or two extension words.

GENERATION: OPERAND GIVEN

ASSEMBLER SYNTAX: #<>>>

EA MODE FIELD: 111

EA REGISTER FIELD: 100

NUMBER OF EXTENSION WORDS: 1,2,4, OR 6, EXCEPT FOR PACKED DECIMAL REAL OPERANDS

D5: 12345678

(1) move,b #\$3A,D5 New D5=?

(2) move.w #\$9E00, D5 New D5=?

(3) move.1 #1, D5 New D5=?

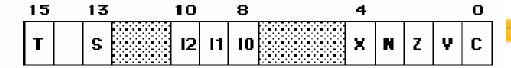

# **CCR** and Condition Code

| Bit | Meaning                                                                  |  |

|-----|--------------------------------------------------------------------------|--|

| Т   | Tracing for run-time<br>debugging                                        |  |

| s   | Supervisor or<br>User Mode                                               |  |

| I   | System responds to interrupts<br>with a level higher than I              |  |

| C   | Set if a carry or borrow is<br>generated. Cleared otherwise              |  |

| V   | Set if a signed overflow<br>occurs. Cleared otherwise                    |  |

| (z) | Set if the result is zero.<br>Cleared otherwise                          |  |

| N   | Set if the result is negative.<br>Cleared otherwise                      |  |

| х   | Retains information from the carry<br>bit for multi-precision arithmetic |  |

### **Condition Codes**

# **\*\*Most instructions affect the state of the five flags**

```

N (Negative flag):№1 (set): MSB of the result is 1 (set)№0 (cleared): otherwise

```

```

move.b #$3F, D0

addi.b #1,D0

3F

01

40 -->0100 0000 N=0

move.b #$7F,D0

addi.b #1,D0

7F

01

80 --> 1000 0000 N=1

```

### **Condition Codes**

### ∠Z(Zero Flag)

Set (1): result equals zero

**区**Clear(1): otherwise

```

Initial value of D0 = 00000003

subi.b #1,D0 ; D0=0000 0002 Z=0

subi.b #1,D0 ; D0=0000 0001 Z=0

subi.b #1,D0 ; D0=0000 0000 Z=1

```

### ∨ (Overflow Flag)

**Set**: a result represents a sign change

```

Word Byte

move.b \#$77, D0 ;D0\Rightarrow0000 0077

MSB=0

V=x

addi.b #3, DO

;D0=0000 007A

MSB=0 V=0

addi.b #9, D0 ;D0=0000 0083

MSB=1 V=1

subi.b #1, D0 ;D0≠0000 0082

MSB=1 V=0

subi.b #4, DO

;D0<del>=</del>0000

007E

MSB=0 V=1

Long Word

```

### **Condition Code**

# **#**C (Carry Flag)

- △Set:

- **区**Carry out of the MSB of the result (addition)

- **⊠**Borrow as a result (subtraction)

○ Clear: otherwise

```

C=x

Addition with 2's

move.b #6, D0 ;D0=0000 0006

C=0

subi.b #1, DO

;D0=0000 0005

complement

00000006

move.b #6, D0 ;D0=0000006

C=x

2's Complement of 9

subi.b #9, D0 ;D0=FFFFFFFD (borrow)

C=1

FFFFFFF7

FFFFFFFD (no carry)

that means there

WAS borrow

```